Generic Computer

|

Group Name: Performance Modeling

Directory: perfmod

|

|

|

Description

The GenericComputer device models the basic functioning of a

computer and collects statistics. The GenericComputer is designed

to behave similarly to any real computer but it simulates a

compute operation with a representative delay instead of an actual

computation. GenericComputers are driven by program files (usually

from compiled DFGs) or instruction lines.

Instructions may be associated with a particular process in the

GenericComputer. If there exist multiple processes in a

GenericComputer, the GenericComputer will interleave execution of

instructions from different processes. This concept is known

multitasking. The way in which the GenericComputer chooses the

next process to execute instructions from is known as

scheduling. The default scheduler in the GenericComputer will

schedule based on the priority of the instructions. The default

scheduler will preempt (interrupt) the current instruction if a

higher priority instruction is send to the processor.

Ports

Input

- instruction lines

Accepts instructions for the computer to

execute. An instruction line may have any name except

"io_in".

- io_in

Input port for arriving messages.

Output

- io_out

Output port for outgoing messages.

Attributes

- speed_up = 1.0

Scales the compute time of instructions.

- boot_time = 0.0ms

The time this computer takes to boot.

- context_switch_time = 0.0ms

The time to switch between processes.

- tcp_send_overhead = 1000.0ms

.

- tcp_per_byte_cost = 1000.0ms

.

Output

- processing timeline

The time to switch between processes.

- utilization

The time to switch between processes.

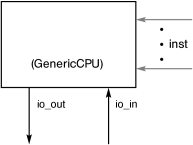

Generic CPU

|

Group Name: Performance Modeling

Directory: perfmod

|

|

|

Description

The GenericCPU device models the basic functioning of a

computer and collects statistics. The GenericCPU is designed to

behave similarly to any real computer but it simulates a compute

operation with a representative delay instead of an actual

computation. GenericCPUs are driven by program files (usually from

compiled DFGs) or instruction lines.

Instructions may be associated with a particular process in the

GenericCPU. If there exist multiple processes in a GenericCPU, the

GenericCPU will interleave execution of instructions from

different processes. This concept is known multitasking. The way

in which the GenericCPU chooses the next process to execute

instructions from is known as scheduling. The default scheduler in

the GenericCPU will schedule based on the priority of the

instructions. The default scheduler will preempt (interrupt) the

current instruction if a higher priority instruction is send to

the processor.

Ports

Input

- instruction lines

Accepts instructions for the CPU to execute. An

instruction line may have any name except "io_in".

- io_in

Input port for arriving messages.

Output

- io_out

Output port for outgoing messages.

Attributes

- speed_up = 1.0

Scales the compute time of instructions.

- boot_time = 0.0

The time this computer takes to boot.

- context_switch_time = 0.0

The time to switch between processes.

Output

- processing timeline

The time to switch between processes.

- utilization

The time to switch between processes.

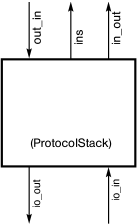

Protocol Stack

|

Group Name: Performance Modeling

Directory: perfmod

|

|

|

Description

Ports

Input

- out_in

Input port for outgoing messages.

- io_in

Input port for arriving messages.

Output

- io_out

Output port for outgoing messages.

- in_out

Output port for arriving messages.

- ins

Output port for cpu instructions.

Attributes

- tcp_send_overhead = 1000.0ms

.

- tcp_per_byte_cost = 500.0ms

.

- udp_send_overhead = 500.0ms

.

- udp_per_byte_cost = 100.0ms

.

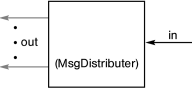

Message Distributer

|

Group Name: Performance Modeling

Directory: perfmod

|

|

|

Description

The MsgDistributer device routes incomming performance model

messages to the output port with a name that matches a particular

field in the message.

Ports

Input

- in

Input port for arriving messages.

Output

- output lines

Output port for outgoing messages.

Attributes

- field

Sets which field to compare the output port names

to.

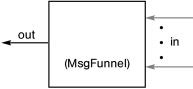

Message Funnel

|

Group Name: Performance Modeling

Directory: perfmod

|

|

|

Description

The MsgFunnel device routes all incomming performance model

messages to a single output port named "out".

Ports

Input

- input lines

Input port for arriving messages.

Output

- out

Output port for outgoing messages.

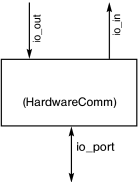

Hardware Communications Device

|

Group Name: Performance Modeling

Directory: perfmod

|

|

|

Description

The MsgFunnel device routes all incomming performance model

messages to a single output port named "out".

Ports

Input

- io_out

Input port for outgoing messages.

- io_port

Input port for arriving messages.

Output

- io_in

Output port for arriving messages.

- io_port

Output port for outgoing messages.

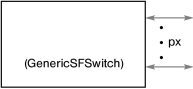

Generic Store & Forward Switch

|

Group Name: Performance Modeling

Directory: perfmod

|

|

|

Description

The MsgFunnel device routes all incomming performance model

messages to a single output port named "out".

Ports

Input

- io_out

Input port for outgoing messages.

- io_port

Input port for arriving messages.

Output

- io_in

Output port for arriving messages.

- io_port

Output port for outgoing messages.

Aron Rubin

Last modified: Mon Apr 9 16:50:21 EDT 2001